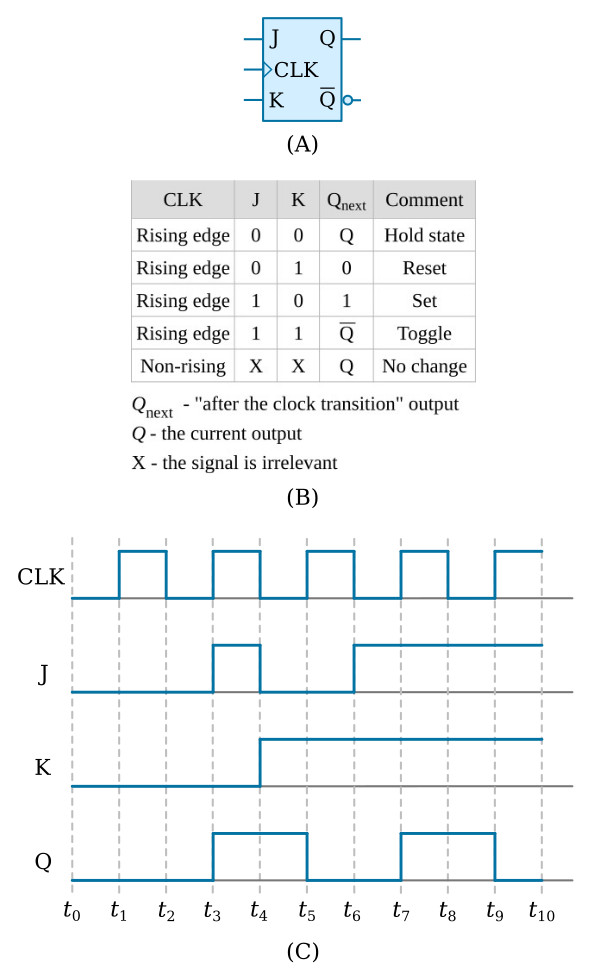

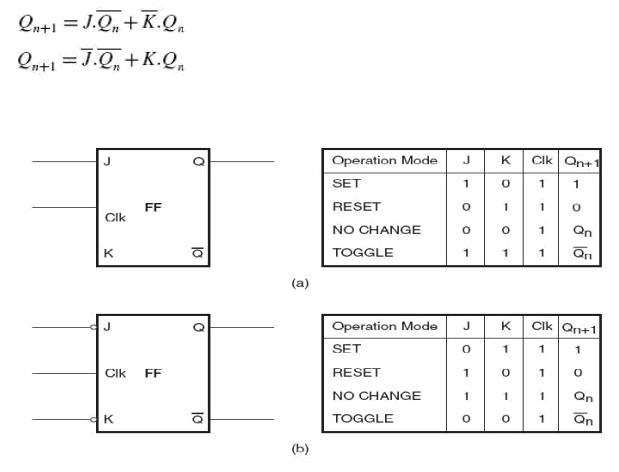

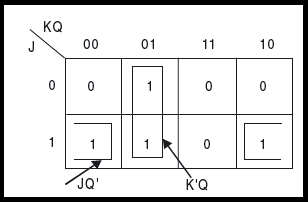

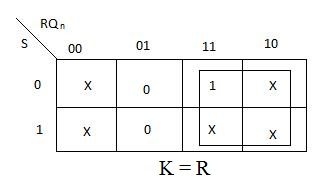

digital logic - drawing flipflop after statement table and kmap simplification - Electrical Engineering Stack Exchange

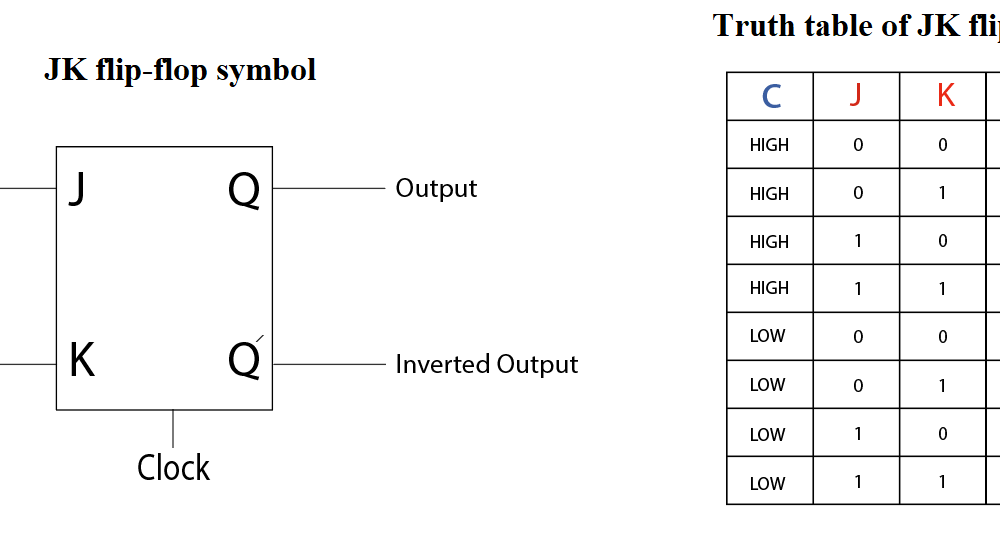

Why does the JK flip-flop toggles on the 'negative edge' of its clock input when its inputs are connected to +v (i.e when j=1 , k=1)? - Quora